Логические элементы оперируют сигналами двух образов: «высокий логический уровень» (1) и «низкий логический уровень» (0), какие характеризуются различным уровнем напряжения: полное напряжение питания принимается в качестве степени «логической единицы», а нулевое напряжение — в качестве уровня «логического нуля».

Логические элементы оперируют сигналами двух образов: «высокий логический уровень» (1) и «низкий логический уровень» (0), какие характеризуются различным уровнем напряжения: полное напряжение питания принимается в качестве степени «логической единицы», а нулевое напряжение — в качестве уровня «логического нуля».

В идеальном случае все сигналы логических элементов были бы в виде этих двух предельных уровней напряжения, и никогда бы от них не отклонялись (так, ниже полного напряжения для «высокого уровня», или выше нуля для «низенького уровня».) Однако в реальности уровни напряжения цифровых сигналов утилитарны никогда не достигают этих идеальных величин.

Вследствие наличия паразитных падений усилия в схемах на транзисторах, наводок, длины линии передачи сигнала и т.д.. Потому для логических схем интерпретируют сигналы как логическую единицу или логический нуль, даже в тех случаях, когда усилие сигналов лежит в диапазоне между полным напряжением питания и нулём, то есть номинально не соответствует ни тому ни другом показателю.

Номинальное напряжение столы для логических радиоэлементов (микросхем) и номинальное значение логического 0 и логической 1

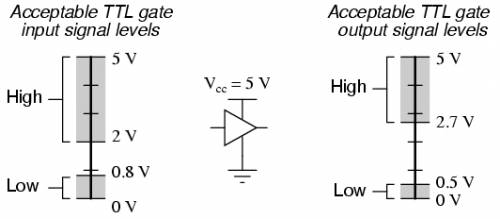

Элементы ТТЛ трудятся при номинальном напряжении питания 5 вольт, +/- 0,25 вольт. В идеале, сигнал рослого логического уровня должен быть равен ровно 5,00 В, а сигнал низенького уровня — ровно 0,00 вольт. Однако в реальных элементах ТТЛ не могут быть гарантированы подобные точные уровни напряжения, поэтому они могут принимать сигналы рослого и низкого уровней даже при значительном отклонении напряжения от идеальных размеров. «Приемлемые» напряжения входного сигнала лежат в диапазоне от 0 до 0,8 вольт для низенького логического уровня, и от 2 до 5 вольт для высокого логического уровня. «Приемлемые» усилия выходного сигнала (уровни напряжения, гарантируемые производителем элемента в показанных вариантах нагрузки) лежат в диапазоне от 0 до 0,5 вольт для низкого логического степени, и от 2,7 до 5 вольт для высокого логического уровня.

Если бы на вход элемента ТТЛ устроился сигнал напряжения в диапазоне от 0,8 до 2 вольт, то мы не получили бы гарантированной реакции схемы. Подобный сигнал будет рассматриваться как неопределённый, и в этом случае ни одинешенек производитель не даст гарантии того, к какому логическому уровню отнесёт схема подобный сигнал.

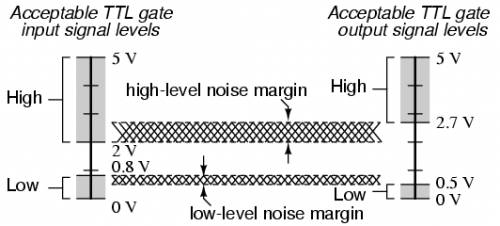

Как вы видаете, диапазон допусков по уровням выходного сигнала меньше, чем в случае для входного сигнала. Это необходимо для обеспечения того, что цифровой сигнал, поступающий с выхода одного элемента логики на вход иного элемента, воспринимался бы таковым же, но с учетом условий потери и воздействия на него. Разница допусков между входным и выходным сигналами именуется запасом схемы по помехоустойчивости. Для ТТЛ-схем, запас помехоустойчивости для низкого логического степени представляет разность между 0,8 В и 0,5 В (т.е. 0,3 В), в то время как резерв помехоустойчивости для высокого уровня равен 0,7 В (2,7 В — 2,0 В). Несложнее говоря, запас помехоустойчивости есть некий запас на паразитное или шумовое усилие, которое может быть наложено на исходный сигнал, прежде чем принимающая схема может неверно его проинтерпретировать.

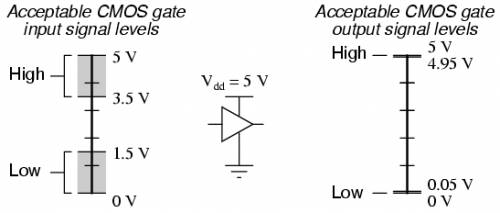

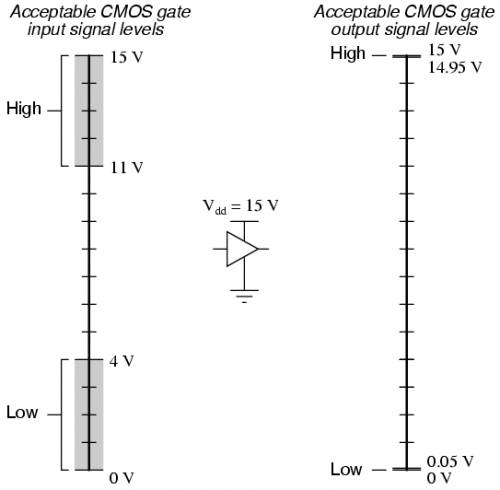

Спецификации входных и выходных сигналов схем КМОП логических элементов совсем отличны от уровней напряжения, используемых для ТТЛ-элементов. Для КМОП-элементов, работающих при усилье питания 5 вольт, приемлемые напряжения входного сигнала лежат в диапазоне от 0 до 1,5 вольт для низенького логического уровня, и от 3,5 до 5 вольт для высокого логического уровня. «Приемлемые» усилия выходного сигнала (уровни напряжения, гарантируемые производителем элемента при показанном варианте нагрузки) лежат в диапазоне от 0 до 0,05 вольт для низкого логического степени, и от 4,95 до 5 вольт для высокого логического уровня.

Представленные значения подают понять, что запас помехоустойчивости КМОП логических элементов гораздо больше аналогичного показателя ТТЛ-элементов: 1,45 вольт как для логического нуля, так и для логической единицы, против максимального запаса в 0,7 В в случае ТТЛ. Другими словами, КМОП-схемы могут вынести более чем вдвое высокий наложенный шум на входе без ошибок интерпретации сигнала как логического нуля или единицы.

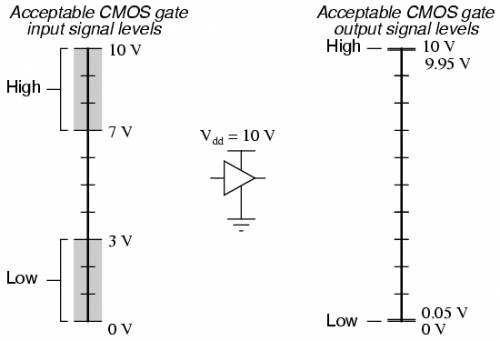

Запас помехоустойчивости КМОП логических схем становится ещё больше при немало высоких рабочих напряжениях. В отличие от элементов ТТЛ, напряжение питания каких не превышает 5 вольт, напряжение питания КМОП-схем может достигать 15 (а в кой-каких случаях и 18) вольт. Ниже показаны приемлемые уровни логических нуля и единицы, для выхода и входа КМОП-ИС, работающих при напряжении питания 10 и 15 вольт соответственно:

Резерв помехоустойчивости может быть выше того, что показано на предыдущем рисунке. На рисунке показан худший из вероятных вариантов поведения сигнала на основании спецификаций производителя. На практике логическая схема может вынести сигналы высокого логического уровня со значительно меньшим напряжением и сигналы низенького логического уровня с гораздо большим напряжением чем указано.

И наоборот, необыкновенно малые показанные запасы помехоустойчивости — гарантирующие выходное состояние сигналов рослого и низкого логических уровней с точностью до 0,05 вольта напряжения столы — практически реальны. Такие «добротные» уровни выходного напряжения будут доступны лишь при минимальной нагрузке. При значительном втекающем или вытекающем токе схемы выходное усилие не будет поддерживаться на этих оптимальных уровнях, что обусловлено наличием внутреннего сопротивления каналов выходных МОП-транзисторов логических элементов.

Помехоустойчивость при единичных (разовых) скачках усилия, появления помехи (наводки)

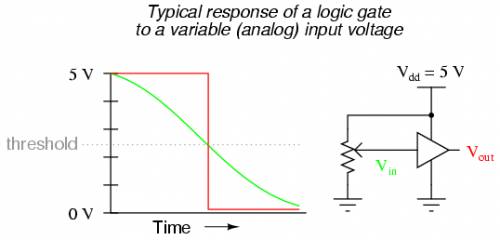

В пределах «неопределённого» диапазона для любого входа логического элемента, будет быть точка разделения актуального сигнала низкого уровня от диапазона действительного входного сигнала рослого уровня. То есть, где-то между наименьшим напряжением сигнала рослого логического уровня и наибольшим напряжением сигнала низкого логического степени гарантированного производителем, существует порог напряжения, при котором логическая схема будет менять интерпретацию сигнала с рослого на низкий и наоборот. В случае большей части логических схем, это усилие соответствует одной определённой точке:

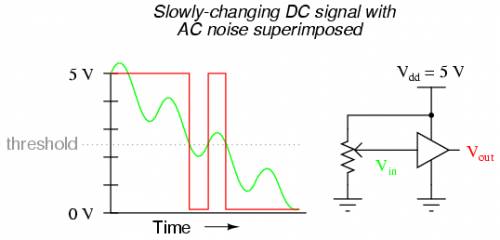

При наличии шумового напряжения переменного тока, наложенного на входной сигнал непрерывного тока единственная точка, в которой схема переменит интерпретацию логического степени будет обуславливать ошибочный сигнал на выходе.

Подобная проблема характерна также для аналоговых ОУ-компараторов усилия. В случае одиночной пороговой точки смены логического уровня присутствие значительного шума может привести к неверной интерпретации логического степени на выходе.

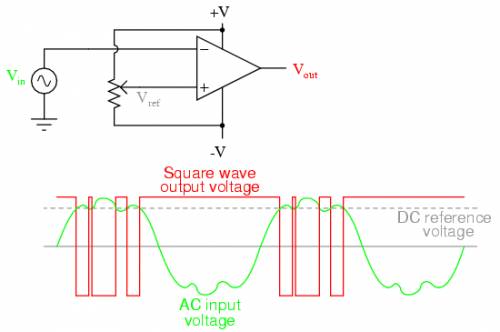

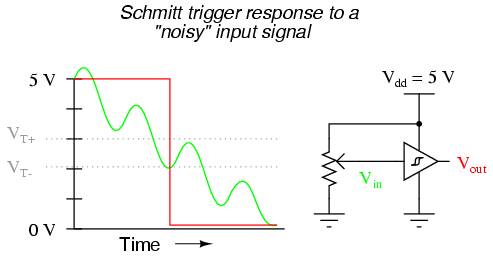

Эту проблему можно решить путём введения в цепь усилителя позитивной обратной связи. В случае операционного усилителя необходимо соединить выход с неинвертирующим входом сквозь резистор. Схемы подобного типа называются триггерами Шмитта. Триггеры Шмитта идентифицируют логический степень сигнала согласно двум пороговым уровням: при нарастающем напряжении (VT+), и при упадающем напряжении (VT-):

На схемах триггеры Шмитта изображаются с символом «гистерезиса». Гистерезис, потребованный положительной обратной связью в схеме логического элемента, придаёт схеме добавочную помехоустойчивость. Триггеры Шмитта часто используются в схемах с высокой вероятностью гула на входе, а также в тех случаях когда ошибочно интерпретированный сигнал на выходе повергнет к некорректной работе системы в целом.

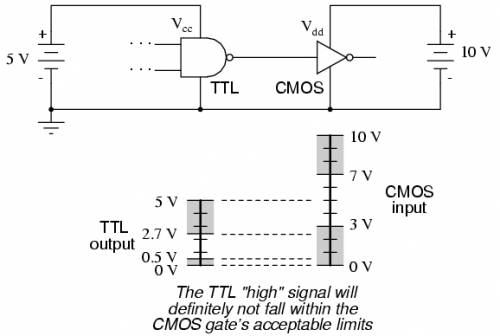

Различные требования по уровням усилия ТТЛ- и КМОП-элементов создают определённые проблемы при использовании в одной схеме элементов двух образов. Хотя работа КМОП логических элементов может осуществляться при том же усилье питания 5,00 В, которое необходимо для элементов ТТЛ, выходные уровни усилия ТТЛ логики несовместимы с входными требованиями по напряжению для КМОП-схем.

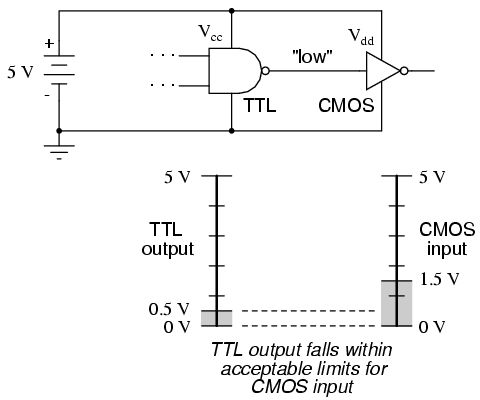

Возьмём к образцу ТТЛ-элемент НЕ-И, сигнал с выхода которого подаётся на вход КМОП-инвертора. Стол обоих элементов составляет 5,00 В (Vcc). Если с выхода элемента ТТЛ приходит сигнал логического нуля (т.е. между 0 и 0,5 В), то он будет неизменно интерпретирован на входе КМОП-схемы как сигнал низкого логического уровня (т.е. сигнал между 0 и 1,5 В):

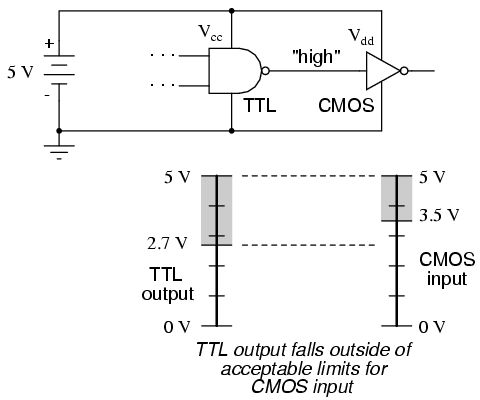

Однако, если с выхода элемента ТТЛ приходит сигнал логической единицы (т.е. между 5 и 2,7 В), то он может быть неверно интерпретирован на входе КМОП-схемы как сигнал рослого логического уровня (т.е. ожидается сигнал между 5 и 3,5 В):

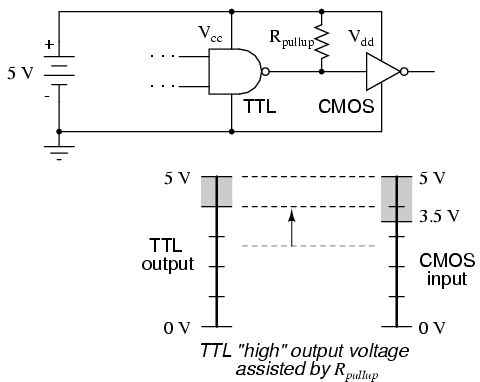

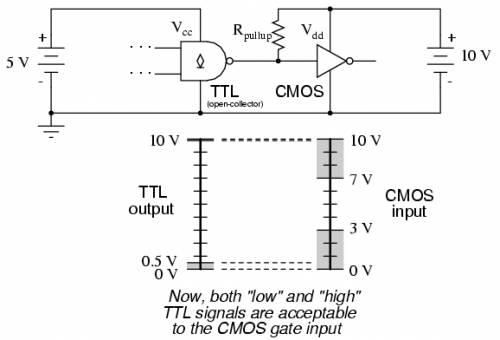

Такое несоответствие может повергнуть к тому, что «правильный» сигнал высокого уровня на выходе ТТЛ- элемента (верный с точки зрения стандартов ТТЛ) будет лежат в «неопределённом» диапазоне входа КМОП-схемы, и быть неверно воспринят как сигнал логического нуля принимающим элементом. Несложным решением этой проблемы может стать повышение сигнала логической единицы элемента ТТЛ с помощью нагрузочного повышающего резистора:

Однако потребуется гораздо немало серьёзная переделка схемы, если питание КМОП-схемы выше 5 вольт:

Проблемы не возникнет в случае логического нуля, однако всё обстоит совсем иначе в случае сигнала высокого логического уровня с выхода элемента ТТЛ. Диапазон выходного усилия 2,7-5 В с выхода элемента ТТЛ совершенно не соответствует приемлемому диапазону 7-10 В КМОП логической схемы. Если мы используем ТТЛ-схемы с отворённым коллектором, то нагрузочный резистор, включённый в шину питания Vdd 10 вольт, возвысит сигнал высокого логического уровня до полного напряжения питания КМОП логической схемы. Поскольку в схеме с отворённым коллектором в наличии только втекающий ток, напряжение логической единицы целиком определяется тем напряжением питания, к которому подключён повышающий резистор, что помогает разрешить проблему несоответствия уровней напряжения.

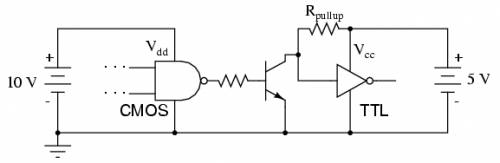

Благодаря прекрасным характеристикам выходного усилия КМОП схем, проблем при подключения ТТЛ элемента к выходу КМОП схемы обыкновенно не возникает. Единственной серьёзной проблемой может стать токовая нагрузка, поскольку КМОП-схема должна обеспечивать втекающий ток на любой вход элемента ТТЛ в случае логического нуля.

Если КМОП-схема столуется от источника напряжения выше 5 вольт (Vcc), то возникнет проблема. Напряжение логической единицы КМОП-схемы выше 5 вольт не будет находиться в диапазоне допустимых входные параметров элемента ТТЛ. Решением этой проблемы может сделаться инвертор с «открытым коллектором» на дискретном NPN-транзисторе, используемом для соединения двух логических схем:

Повышающий резистор Rpullup используется опционально, поскольку входы элементов ТТЛ принимают рослый логический уровень, когда находятся в плавающем состоянии, что и произойдёт, когда выход КМОП-схемы будет низеньким, а транзистор будет находиться в состоянии отсечки. Конечно, важным последствием такого решения является логическая инверсия, основываемая транзистором: когда на выходе КМОП-схемы будет сигнал логического нуля, элемент ТТЛ будет «видать» логическую единицу и наоборот. Однако, если принимать эту инверсию во внимание, то корректная труд схемы не будет нарушена.